# CPE 2211 COMPUTER ENGINEERING LAB EXPERIMENT 7 LAB MANUAL

Revised: J. Tichenor FS19

#### HIERARCHICAL DESIGN OF A FOUR BIT ADDER

#### **OBJECTIVES**

In this experiment you will

- Explore more advanced features of schematic based design.

- Gain experience with hierarchical design.

- Gain experience with four bit adder.

- Use the suite of EDA tools supplied by Altera: Quartus-II and ModelSim.

#### LAB REPORTS

The format of lab reports should be such that the information can be used to reproduce the lab, including what values were used in a circuit, why the values were used, how the values were determined, and any results and observations made. This lab manual will be used as a guide for what calculations need to be made, what values need to be recorded, and various other questions. The lab report does not need to repeat everything from the manual verbatim, but it does need to include enough information for a 3<sup>rd</sup> party to be able to use the report to obtain the same observations and answers. Throughout the lab manual, in the Preliminary (if there is one), and in the Procedure, there are areas designated by **Qxx followed by a question or statement**. These areas will be **bold**, and the lab TA will be looking for an answer or image for each. These answers or images are to be included in the lab report. The lab TA will let you know if the lab report will be paper form, or if you will be able to submit electronically.

#### REFERENCES

Tutorial: Quartus II and ModelSim

#### **PRELIMINARY**

Read through the tutorial to familiarize yourself with the steps you will be performing. Construct a truth table for the circuit in Figure 1 of the tutorial and verify to yourself that it represents a full adder circuit.

#### **PROCEDURE**

Work through the tutorial in the lab. Take notes as you are going through the procedures. Answer the questions below and submit them together with hardcopies of the schematic along with any other material your TA might require.

- Q1. Why is it not important which signal goes to which input of a full adder?

- **Q2.** Actually there is a slight difference between full adder inputs. What is the difference between the A, B, and C inputs shown in Figure 1 of the tutorial?

- **Q3.** What is a symbol?

- **Q4.** What is the purpose of a bus?

- **Q5.** The tutorial led you through bottom up design. Briefly describe the procedure you would use for top down design.

# TUTORIAL: More Quartus II Purpose

The purpose of this exercise is to introduce you to *hierarchical design* and more advanced functions in Quartus II. You will design the symbol and schematic for a full adder component and then instantiate that component in another schematic in order to implement a four bit ripple carry adder. You will also be introduced to buses which are like subscripted variables in a programming language.

The kind of hierarchical design explored in this tutorial is sometimes called *bottom up design* since the design will start with a low level component and then use that in a higher level design. Symbols representing the lower level component, will be used for the low level design instead of creating multiple copies of its schematic in order to reduce the complexity of the higher level design. Schematics which consist of symbols which represent other lower level schematics are often called hierarchical schematics or designs as opposed to flat schematics which consist entirely of primitive components such as gates and flip flops. A *top down* design could have been used, where the design methodology creates a top level symbol and then the underlying schematics instead of *bottom up* design where the design starts with schematics and then creates symbols.

When you are finished with this exercise you should have a solid understanding of the basics of schematic capture and logic simulation with ModelSim. While you won't be an expert you will be well on your way toward becoming one and should be able to explore the basics and more advanced features of FPGA design tools in depth on your own using the online reference and user's manuals.

## **Getting Started**

After creating a new project named lab7 in Quartus II, the first task will be to design a full adder component for the four bit adder. In the Quartus II display select **File | New**. Since you will be using the schematic-entry approach in this section, choose **Block Diagram/Schematic File** and click OK.

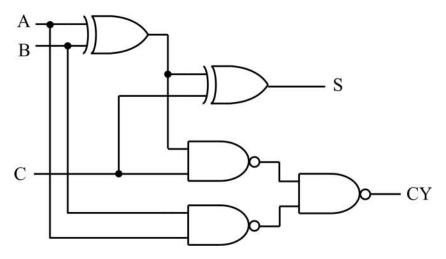

A logic diagram for a full adder is shown in Figure 1. You should convince yourself that functions S and CY do in fact implement the Sum and Carryout functions of a full adder. S is straightforward and is high (1) whenever there are an odd number of input lines high. CY is not quite as obvious but is high whenever A and B are high or C and one of A or B is high. This

realizes the function AB + CAB' + CBA', which is the carry out function of a full adder.

Figure 1: Full Adder Schematic.

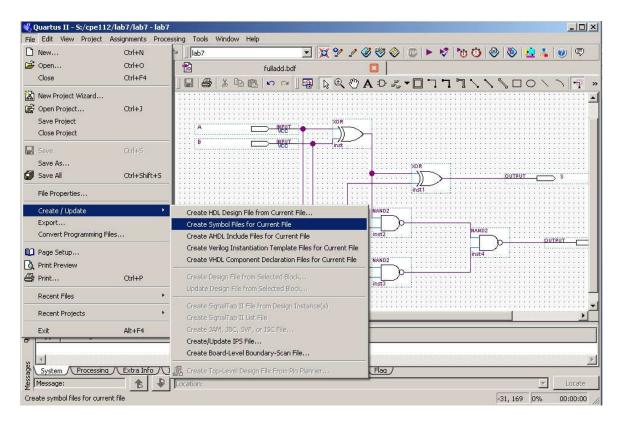

Save this file with the name fulladd. Once getting successful compilation, go to **File**, click **Create/Update** and **Create Symbol Files for Current File** as shown in Figure 2. This symbol will be used in the four bit adder.

### Four Bit Adder Design

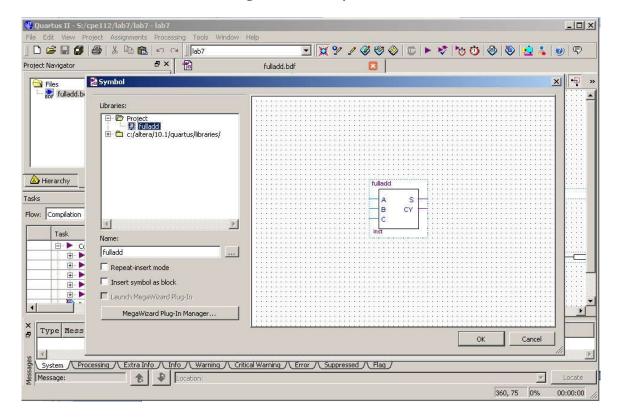

Create a new Block Diagram/Schematic File. To import the schematic symbols, double-click on the Block Editor screen, or select **Edit | Insert Symbol**. This command opens the window in Figure 3. Click on the + next to the label Project on the top-left of the figure, and then click on the item *fulladd* to select this symbol. Click OK to import the symbol into the schematic.

Figure 2: Create Symbol.

Figure 3: Insert Symbol.

Buses are nothing more than nets with a special naming syntax and correspond physically to a bundle of wires or like a subscripted variable in a programming language like C or FORTRAN. Normally buses are shown on a schematic as a line segment that is a little fatter than a normal net but that is purely for visual purposes. In general all buses must have a name. The system must be told somehow that a particular net corresponds to more than one wire and the name is the only way we have for doing that at the moment. The orthogonal and diagonal bus tool can be found at the top of the schematic screen.

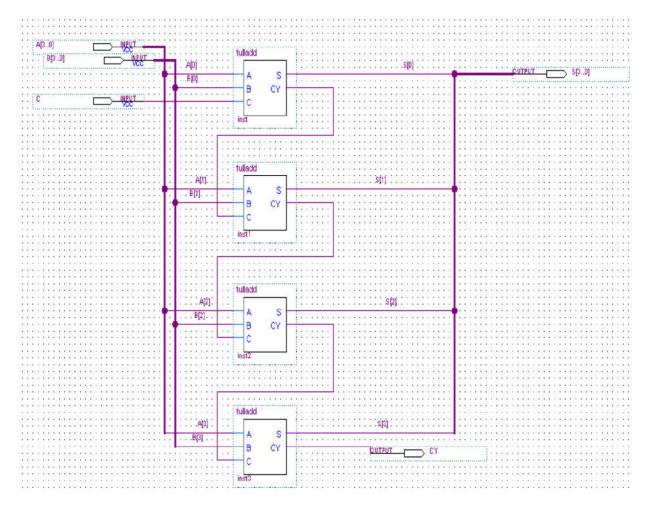

Add an Input Port to each input bus and name them A[3..0] and B[3..0]. The bus naming convention consists of a netname (A or B) and a subscript range in parentheses. By convention the subscript on the right is the LSB so that if for example, the bus A[3..0] means that A[3] is high and bits A[2..0] are low. Also, notice that each wire connected into a bus has to be assigned a name such as A[3], A[2], A[1] and A[0]. The same thing needs to be done with the output S[3..0]. Finally, the circuit is shown in Figure 4.

Figure 4: Final circuit schematic.

Save this file with the name lab7. Once getting successful compilation, go to **File**, click **Create/Update and Create HDL Design File from Current File** for both lab7.bsf and fulladd.bsf. The two VHDL file are lab7.vhd and fulladd.vhd.

#### Simulation

Start the Modelsim software. Create a new project named lab7. And add both lab7.vhd and fulladd.vhd as the existing files into the project. After the compilation of all files, start simulating this design by generating waveforms to be applied to the C, A, and B signals. Since both A and B are four bit signals, you want to exercise all 512 combinations of 9 (4+4+1) bits and let A cycle through its 16 combinations, then change B and so on. After cycling through 256 combinations of A and B, set C to one and repeat it all again for a total of 512 events.

In the wave window, left click on the "+" of input "a", then right click on "(0)" and select clock. After setting the period to be 100 and first edge to be **Falling**, click on OK. Repeat this procedure for the inputs "(1)", "(2)" and "(3)" with setting the periods to be 200, 400 and 800 respectively. Then do the same thing for input signal "b", set the clock periods for "(0)", "(1)", "(2)" and "(3)" to be 1600, 3200, 6400, and 12800. Lastly, select C and set its clock period to be 25600. Then type **run 51200 ps**, you should be able to see the simulation waveform. Also, if you want to view the hexadecimal format of the input and output, select A, B and S, and click on format/radix/hexadecimal.